摘要:基于FPGA和DSP芯片相结合的方式,设计了一种基于高性能数字信号处理器的雷达回波信号处理系统。该系统通过对雷达的回波信号进行实时计算以得出被测物的实际距离。系统结合了FPGA和DSP两种芯片各自的优势,极大地提高了系统数据处理的能力,以实现实时准确的物位测量。

引言

伴随着数字技术的进步,雷达测距技术在近年也得到了快速发展。与此同时,实际应用中对于雷达测距技术的性能和精度要求也在不断提高。

雷达物位计的信号处理普遍采用数字信号处理的方法,利用诸如DSP、FPGA等高速信号处理芯片,可使雷达信号处理能力得到大幅提升。传统的雷达物位计采用DSP芯片来处理和控制信号,这种方法已经在雷达技术领域得到了广泛的应用[1]。本文主要介绍一种结合了DSP芯片和FPGA芯片各自优势的雷达物位计信号处理方法。主要采用的是DSP芯片TMS320F28335和XILINX公司的Virtex-4系列的FPGA芯片,通过灵活的配置,充分利用了两块芯片的内部资源,兼顾了灵活性和速度,大大提高了雷达物位系统的性能。

1处理器介绍

FPGA芯片使用的是XILINX的Virtex-4芯片。该芯片的主频可达到500MHz,非常适合高速数据处理应用。它的基本构成是一个四通道LUT、一个触发器、一个功能扩展器(MUXF)以及一个算法单元(MULT_AND)。在RAM工作模式下,该芯片的LUT可用作一个十六位的存储单元或者一个十六位的移位寄存器[2]。本设计选用的DSP芯片是TMS320C6416。该芯片是zui新一代的高性能DSP芯片,其核心频率高达600MHz,zui高处理能力为4800MIPS,软件能够与C6X系列实现完全兼容,其内核有6个ALU(32/40bit),每个时钟周期可以执行8条指令[2]。相较于C6X系列的其他芯片,TMS32OC6416有着诸多显著区别,其数据处理能力的大幅提升,达到了4800MPIS,是早期C6201芯片处理能力的3倍,执行1024点复数FFT的速度比C6201快了大约6倍[1]。2FPGA+DSP信号处理系统的优势由于FPGA和DSP各有优势,因此两者之间可以相互配置。通常情况下,DSP作为系统的主控制器。FPGA上电后由DSP来完成配置。在系统运行过程中,DSP作为主控制芯片,在必要时可以对FPGA进行重新配置。

虽然从整体成本角度考虑,单芯片系统是zui优的设计方案,但是如果采用单芯片,无论是FPGA还是DSP,都会使设计开发的难度大幅提升。采用FPGA+DSP的设计方案虽然材料成本高于单芯片方案,但是系统的设计开发难度和时间都优于前者。因此,降低了系统开发的技术风险,是一种在材料成本和开发成本两者之间的折中选择。

3设计方案和主要组成部分

3.1系统的方案设计

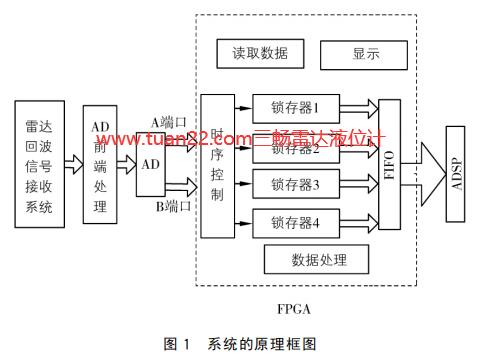

本文设计的雷达物位计的信号处理系统的组成主要包括AD采样部分、可编程FPGA部分和DSP信号处理部分。该系统的设计采样频率可达10MHz,而且集数据采集信号与处理于一体,可实现实时触发、延迟触发和超前触发三种触发模式。本系统主要应用于较小型的雷达物位测量设备,小型雷达系统主要通过对激光回波信号的快速捕获与检测,计算出雷达物位计天线与被测物体的实时距离。详细系统框图如图1所示。

模拟量转换前端设计在本设计电路中,用于放大、衰减信号和匹配阻抗,这样输入信号即可满足ADC的要求。DSP的特点是它具有非常快速的信号处理速度,单DSP的输入仅限数字信号形式,所以需要先通过9841高速A/D转换器对模拟信号进行转换。转换器的工作模式设定为双通道数字输出模式,9841具有相应的功能选择[3]。从双通道输出的数据和动态比较器会首先锁存差分时钟,这样,之前采样转换后得到的数据频率变成原来的1/2。之后缓存到FIFO中,当缓存满时,FIFO会向DSP申请中断,DSP响应申请,通过组数据传输对数据进行读取并存储到内存中以便实时处理。FPGA在系统当中就是各个子功能模块的集成,诸如锁存、时序、控制部分等功能因此得以集中。对于不同系统的不同功能需求,可以对功能块进行参数修改、整体应用,这是FPGA功能块移植性好的优点。由于高速数模转换器的工作状态需要一定时间才能进入稳定状态,其工作状态一旦经常改变就会影响结果的精度,因此常规系统的数模转换器在高速系统中并不适用。本设计采用的是选通采样,即同步命令控制FIFO写入端,决定其是否可以写入,以此达到对采样数据进行取舍的目的。在应用过程中,当激光脉冲信号产生,一直处于工作状态的数模转换器和时钟电路,选通门同步打开,允许向FIFO写入,等待FIFO缓存满则禁止继续写入,直到下一个脉冲到来,在每一次脉冲到来的周期内都反复一次,这样就完成了选通采样,选通门内的信号即回波信号。这种选通采样对于提升系统稳定性、降低干扰的效果明显。

3.2FPGA模块的工作原理及结构设计

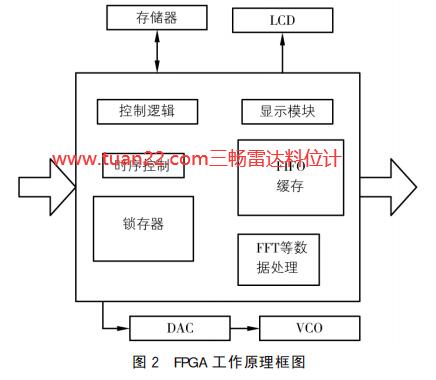

FPGA具有极快的运算速度,IO延时小,因其处理数据是通过硬件来实现的。但是由于FPGA自身构成的特点,FPGA在做混合运算、大量的复杂运算以及浮点运算时,与DSP比较却相形见绌。为充分利用DSP在软件编程上的高灵活性和FPGA在硬件编程上的高效形,本设计将两种方式结合,实现优势互补。FPGA在系统中的主要作用是打包数采数据形成帧格式,产生系统全部时序以及控制逻辑。设计中所有的时序和控制逻辑统一由FPGA产生,读取数据波形并发送至DAC进行转换,然后利用锯齿波调制电压来控制VCO的电压调制端口,使得VCO输出频率为24.2~25.2GHz的线性调频信号[2]。系统中对于采集到的数据的存储、处理和系统工作时序,均由FPGA来完成。在小型高速数采系统中,利用FPGA的强大缓存功能以及更简化的布线,可以使得整个电路系统模块清晰、简化、高效。FPGA模块的结构框图如图2所示。数模采样结束后,数据经锁存器锁存,FIFO对其进行缓存输出。

仿真工具选择ISE自带的仿真软件,设置输入输出信号,完成仿真如图3所示。3.3DSP模块的工作原理该系统的实时控制主要由DSP来完成。为了使信号处理速度进一步提升,应对程序进行进一步优化。选择DSP作为主控芯片时需要充分考虑运算速率和总线位宽的需求。DSP的标准工作流程是,首先初始化,在收到触发信号后,数据采集模块开始工作,然后进入等待状态。此时FPGA开始数据采集,当FIFO写满后,DSP接收到FIFOfull中断信号,停止FIFO写入,同时DSP开始读取FIFO中的数据,并对读取数据进行计算处理。

4数据处理

数据处理时首先要通过数字式相消器抑制地物杂波,然后再通过快门限恒虚警处理得到门限电压,zui后对超过门限电压的采样点进行比较,选择出量值zui高的采样点并对该采样点位置的雷达物位计回波信号中包含的频率信息进行提取,从而计算出目标距离[4]。系统采集到的差拍信号经数模转换后输出数字信号,该数字信号先缓存在FPGA的外部扩展存储器中,当采集满1024点后,运行一次快速傅里叶变换运算,此运算由FPGA完成。得到频率后经计算得出测量距离。

在实际应用中可以根据需要进行设置,当被测物的距离小于某一阈值时,系统会自动发出报警信号。为了降低信号干扰,本设计还结合了数字FIR滤波措施。

5结语

本系统充分利用了可编程逻辑控制器件FPGA和数字信号处理器DSP的高速、可编程、计算能力强、数据处理速度快的优势,快速地完成了对雷达物位计回波信号的数据实时处理,实时提取出雷达回波信号中包含的频率信息,并计算出目标物体的距离,实现了雷达物位计系统的高效高性能。

上一篇:全球雷达液位计市场预计将达到7.037亿美元

下一篇:Drexelbrook扩大了用于导波雷达液位计测量的同轴传感器的范围

销售总机

0517-86998326

销售总机

0517-86998326

图文传真

0517-86998327

图文传真

0517-86998327

电子邮箱

jssanchang

电子邮箱

jssanchang